Pagrindinis trūkumas kombinacinė grandinė tai yra, ji nenaudoja jokios atminties dabartinei ir ankstesnėms būsenoms išsaugoti. Taigi ankstesnė įvesties būsena neturi jokios įtakos dabartinei grandinės būsenai. Kadangi nuoseklioji grandinė turi atmintį, todėl išvestis gali skirtis priklausomai nuo įvesties. Šio tipo grandinėse naudojamas ankstesnis įvestis, išvestis, laikrodis ir atminties elementas. Čia atminties elementai gali būti fiksatoriai arba šlepetės. Nuoseklios grandinės suprojektuotos įvairiais metodais, pavyzdžiui, naudojant ROM ir apverstus, PLA, CPLD (sudėtingas programuojamas loginis įrenginys) , FPGA (lauko programuojamas vartų masyvas) . Šiame straipsnyje aptarsime tik tai, kaip sukurti nuoseklią grandinę naudojant PLA.

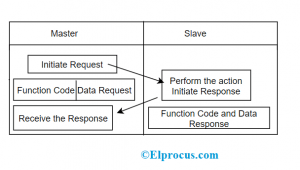

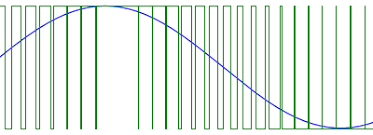

Sekvencinės grandinės blokinė schema, kaip parodyta žemiau:

Nuoseklios grandinės blokinė schema

Nuoseklios grandinės projektavimas naudojant PLA

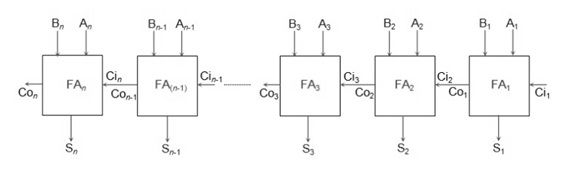

Nuoseklios grandinės galima realizuoti naudojant PLA (programuojamos logikos masyvus) ir šlepetes. Šiame projekte būsenos priskyrimas gali būti svarbus, nes naudojant gerą būsenos priskyrimą galima sumažinti reikiamą gaminių terminų skaičių ir taip sumažinti reikiamą PLA dydį. Produkto terminas, apibrėžtas kaip pažodžių junginys, kur kiekvienas literalas yra arba kintamasis, arba jo neigimas.

Apsvarstykime kodo keitiklio dizainą. Būklės lentelę, parodytą žemiau lentelėje, galima realizuoti naudojant vieną PLA ir tris šlepetės kaip parodyta žemiau paveiksle. Ši grandinės konfigūracija yra labai panaši į ROM „flip-flop“ dizainą, išskyrus tai, kad ROM pakeičiama tinkamo dydžio PLA. Būsenos priskyrimas veda prie toliau pateiktos tiesos lentelės. Ši lentelė galėtų būti saugoma PLA su keturiais įvestimis, 13 produkto sąlygų ir keturiais išvestimis, tačiau tai būtų šiek tiek mažesnė, palyginti su 16 žodžių ROM.

| X Q1 Q2 Q3 | Su D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Lentelė: Tiesos lentelė

PATEIKTI VALSTYBĖ

| KITA VALSTYBĖ X = 0 1 | PATEIKTI IŠĖJIMAS (Z) |

| Į | B C | 1 0 |

B C | D E Ir E | 1 0 0 1 |

D IS | H H H M | 0 1 1 0 |

H M | A A Į - | 0 1 1 - |

Lentelė: būsenos lentelė

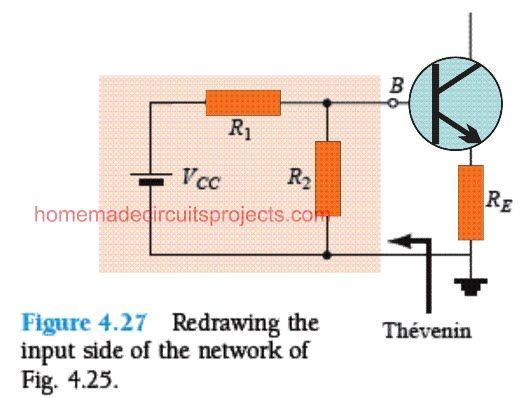

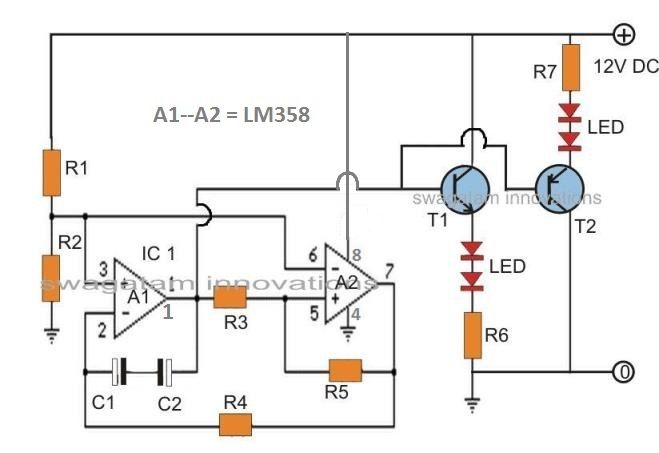

Nuoseklių grandinių projektavimas naudojant PLA

Karnaugh Map gautos įvesties išvesties lygtys

Kadangi yra septynios būsenos, reikalingi trys D šlepetės. Taigi reikalinga PLA grandinė su 4 įėjimais ir 4 išėjimais. Jei atsižvelgiama į kodų keitiklio būsenos priskyrimą, gautą išvesties lygtį ir D „flip-flop“ įvesties lygtis, gautas iš Karnaugh, galima parašyti šias lygtis

D1 = Q1 + = Q2 “

D2 = Q2 + = Q2 “

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 “Q2”

Z = X „Q3“ + X Q3

| X Q1 Q2 Q3 | Su D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 vienuolika

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

PLA lentelė, atitinkanti šias lygtis, pateikta aukščiau esančioje lentelėje. Ši lentelė gali būti realizuota naudojant PLA su keturiais įėjimais, septyniais produkto terminais ir keturiais išėjimais. Norėdami iš pradžių patikrinti aukščiau pateikto projekto veikimą, tarkime, kad X = 0 ir Q1Q2Q3 = 000. Taip lentelėje parenkamos eilutės - - 0- ir 0 - - -0, taigi Z = 0 ir D1D2D3 = 100. Po aktyvaus laikrodžio krašto Q1Q2Q3 = 100. Jei kitas įėjimas yra X = 1, tada pasirenkamos eilutės - - 0 - ir - 1-, taigi Z = 0 ir D1D2D3 = 110. Po aktyvaus laikrodžio krašto Q1Q2Q3 = 110.

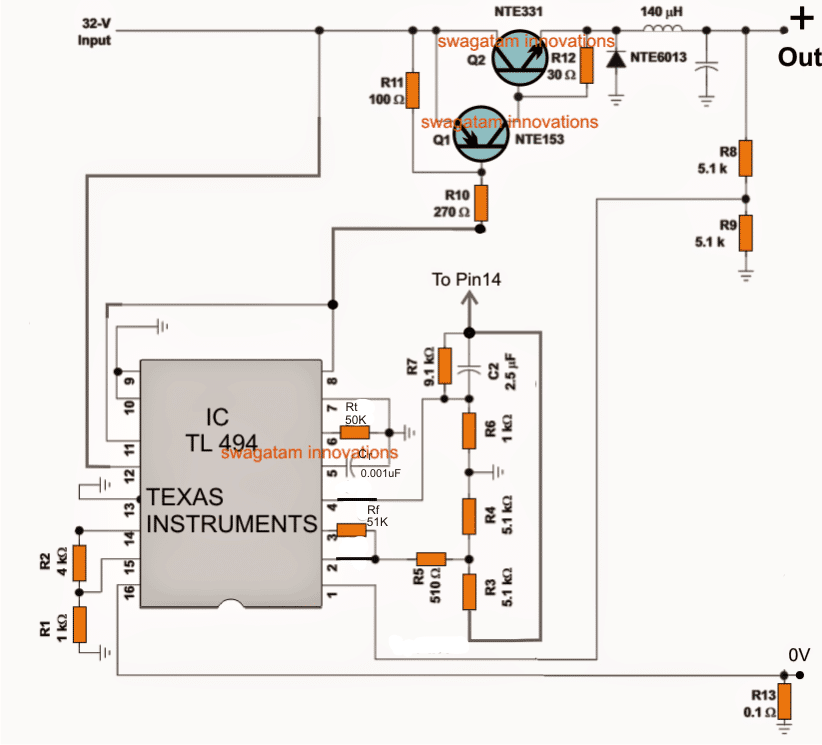

Programuojamas logikos matrica (PLA)

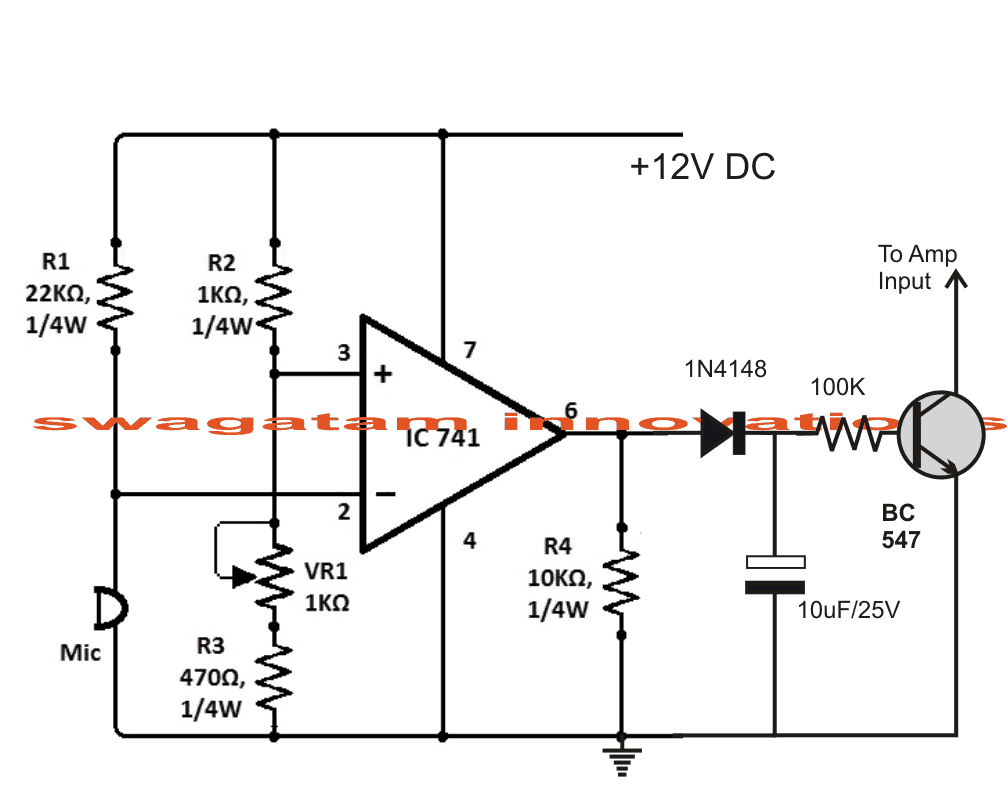

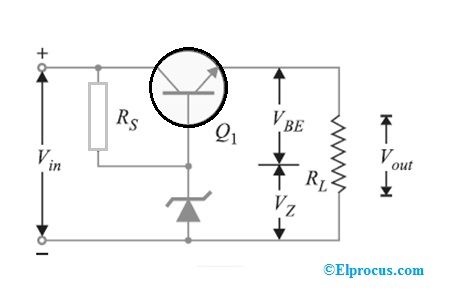

Programuojamas logikos masyvas yra programuojamas loginis įrenginys. Paprastai jis naudojamas kombinuotoms loginėms grandinėms įgyvendinti. PLA turi programuojamų IR plokštumų rinkinį (AND masyvą), susiejančius su programuojamų ARBA plokštumų rinkiniu (OR masyvu), kuriuos vėliau galima laikinai papildyti, kad būtų sukurta išvestis. Šis išdėstymas leidžia daugelį loginių funkcijų susintetinti programoje produktų suma (SOP) kanoninės formos. Toliau pateikiama paprasta PLA blokinė schema.

Blokinė PLA schema

Pagrindinis skirtumas tarp PLA ir PAL (programuojamos masyvo logikos) yra,

PLA: abu IR plokštuma ir ARBA plokštuma yra programuojami.

PAL: Programuojama tik IR plokštuma, o OR plokštuma yra fiksuota.

Norėdami geriau suprasti PLA, čia mes svarstome žemiau pateiktą pavyzdį.

Pabandykime įgyvendinti šias funkcijas f1 ir f2 pateikiamos kaip

X1, x2, x3 įėjimai ir jų atitinkami papildomi signalai yra suteikiami programuojamai IR plokštumai, ten gausime IR plokštumos išėjimus kaip P1, P2, P3, vadinamus mintermais. Tada šie signalai perduodami programuojamai ARBA plokštumai, kad gautų reikiamą išėjimo funkciją f1 ir f2 (produktų suma). Žemiau pateiktame paveiksle aprašomas PLA vartų lygio įgyvendinimas tam tikram funkcionalumui.

PLA įgyvendinimas

Tai viskas apie nuoseklių grandinių projektavimą naudojant PLA. Manome, kad šiame straipsnyje pateikta informacija yra naudinga jums geriau suprasti šią koncepciją. Be to, bet kokie klausimai dėl šio straipsnio ar bet kokia pagalba įgyvendinant elektros ir elektronikos projektus , galite kreiptis į mus komentuodami žemiau esančiame komentarų skyriuje. Štai jums klausimas, Ką reiškia nuosekli grandinė?