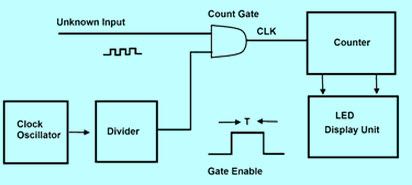

Skaitiklis yra skaitmeninis prietaisas, o skaitiklio išvestyje yra iš anksto nustatyta būsena, pagrįsta laikrodžio impulso programomis. Išvestis skaitiklis gali būti naudojamas suskaičiuoti impulsų skaičių. Paprastai skaitikliai susideda iš „flip-flop“ išdėstymo, kuris gali būti sinchroninis skaitiklis arba asinchroninis skaitiklis. Sinchroniniame skaitiklyje visiems flip-flopams suteikiamas tik vienas laikrodis i / p, o asinchroniniame skaitiklyje o / p šnipštas yra laikrodžio signalas iš netoliese esančio. Programos mikrovaldiklis reikia suskaičiuoti išorinius įvykius, tokius kaip tikslus vidinio laiko uždelsimo generavimas ir impulsinių traukinių dažnis. Šie įvykiai dažnai naudojami skaitmeninėse sistemose ir kompiuteriuose. Abu šie įvykiai gali būti vykdomi programinės įrangos metodais, tačiau skaičiavimo programinės įrangos kilpos tikslaus rezultato neduos, o svarbesnės funkcijos nėra atliekamos. Šias problemas galima pašalinti laikmačiais ir skaitikliais mikrovaldikliuose, kurie naudojami kaip pertraukikliai.

Skaitikliai

Skaitiklių tipai

Skaitliukus galima suskirstyti į skirtingus tipus pagal jų laikrodžio būdą. Jie yra

- Asinchroniniai skaitikliai

- Sinchroniniai skaitikliai

- Asinchroniniai dešimtmečio skaitikliai

- Sinchroniniai dešimtmečio skaitikliai

- Asinchroniniai aukštyn-žemyn skaitikliai

- Sinchroniniai „Up-Down“ skaitikliai

Norėdami geriau suprasti šio tipo skaitiklius, čia aptariame keletą skaitiklių.

Asinchroniniai skaitikliai

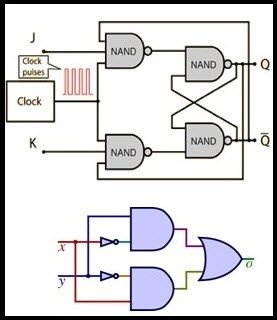

2 bitų asinchroninio skaitiklio schema parodyta žemiau. Išorinis laikrodis prijungtas tik prie FF0 (pirmasis flip-flop) laikrodžio i / p. Taigi, šis FF keičia būseną kiekvieno laikrodžio impulso mažėjančiame krašte, tačiau FF1 pasikeičia tik tada, kai jį įjungia mažėjantis FF0 Q o / p kraštas. Dėl vientisos sklaidos vėlavimo per FF, i / p laikrodžio impulso pasikeitimas ir FF0 Q o / p pokytis niekada negali įvykti tiksliai tuo pačiu metu. Taigi, FF negalima vienu metu aktyvuoti, generuojant asinchroninę operaciją.

Asinchroniniai skaitikliai

Atkreipkite dėmesį, kad patogumui aukščiau pateiktoje diagramoje Q0, Q1 ir CLK pokyčiai rodomi kaip vienu metu, net jei tai yra asinchroninis skaitiklis. Tiesą sakant, yra nedidelis vėlavimas b / n Q0, Q1 ir CLK pokyčiai.

Paprastai visi CLEAR i / ps yra sujungti kartu, todėl prieš pradedant skaičiuoti, tada vienas impulsas gali išvalyti visus FF. Laikrodžio impulsas, tiekiamas į FF0, po vėlavimo plinta per naujus skaitiklius, pvz., Pulsavimą ant vandens, taigi terminas „Ripple Counter“.

Dviejų bitų pulsacijos skaitiklio schema apima keturias skirtingas būsenas, kurių kiekviena susideda iš skaičiaus vertės. Taip pat skaitiklis su n FF gali turėti 2N būsenas. Būklių skaičius skaitiklyje vadinamas jo mod numeriu. Todėl dviejų bitų skaitiklis yra mod-4 skaitiklis.

Asinchroniniai dešimtmečio skaitikliai

Ankstesniame skaitiklyje turi 2n būsenas. Bet taip pat yra galimi skaitikliai, kurių būsenos yra mažesnės nei 2n. Jie yra sukurti taip, kad ne. iš jų serijos būsenų. Tai vadinama sutrumpintomis sekomis, kurios pasiekiamos varant skaitiklį perdirbti prieš pereinant visas jo būsenas. Bendras skaitiklių su sutrumpinta seka modulis yra 10. Skaitiklis su 10 būsenų savo serijoje vadinamas dešimtmečio skaitikliu. Įdiegta dešimtmečio skaitiklio grandinė pateikiama žemiau.

Asinchroninė dešimtmečio skaitiklio grandinės schema

Kai skaitiklis suskaičiuos iki dešimties, visi FF bus išvalyti. Atkreipkite dėmesį, kad tik Q1 ir Q3 naudojami dekoduoti 10 skaičių, tai vadinama daliniu dekodavimu. Tuo pačiu metu viena iš kitų būsenų nuo 0 iki 9 turi Q1 ir Q3. Dešimtmečio skaitiklių lentelės serijos pateikiamos žemiau.

Dešimtmečio skaitiklio seka

Asinchroniniai aukštyn-žemyn skaitikliai

Visų pirma, skaitiklis turi sugebėti skaičiuoti aukštyn ir žemyn. Žemiau esanti grandinė yra trijų bitų aukštyn ir žemyn skaitiklis, kuris skaičiuojamas aukštyn arba žemyn, remiantis valdymo signalo būsena. Kai UP i / p yra 1, o DOWN i / p yra 0, NAND vartai tarp FF0 ir FF1 pateks į apversto šnipšto (FF0) neapverstą o / p (Q) į laikrodį i / p šnipštas (FF1). Panašiai ir neapverstas „Flip Flop1“ o / p bus nukreiptas per kitus NAND vartus į „flip-flop2“ laikrodį i / p. Todėl skaitiklis suskaičiuos.

Asinchroninė aukštyn-žemyn skaitiklio grandinės schema

Kai valdymo i / p (UP) padėtis yra 0 ir žemyn yra 1, apverstos „flip-flop0“ (FF0) ir „flip-flop1“ (FF) apverstos o / ps atskirai nukreipiamos į FF1 ir FF2 laikrodžio i / ps . Jei FF iš pradžių pakeičiama į 0, tada skaitiklis eis per toliau pateiktas serijas, kai bus taikomi i / p impulsai. Atkreipkite dėmesį, kad asinchroninis aukštyn-žemyn skaitiklis yra lėtesnis nei UP skaitiklio / žemyn skaitiklis, dėl papildomo skleidimo vėlavimo, kurį įvedė NAND vartai.

Asinchroninio aukštyn-žemyn skaitiklio seka

Sinchroniniai skaitikliai

Šiame skaitiklių tipas , visų FF CLK i / ps yra sujungtos ir aktyvuojamos i / p impulsais. Taigi visos FF keičia akimirksniu būsenas. Žemiau esanti schema yra trijų bitų sinchroninis skaitiklis. „Flip-flop0“ įėjimai J ir K yra prijungti prie HIGH. „Flip-flop 1“ J & K i / ps yra prijungtas prie „flip-flop0“ (FF0) o / p, o „flip-flop2“ (FF2) įėjimai J & K yra prijungti prie „AND gate“ maitinamas „flip-flop0“ ir „flip-flop1“ o / ps. Kai abu FF0 ir FF1 išėjimai yra aukšti. Teigiamas ketvirtojo CLK impulso kraštas paskatins FF2 pakeisti savo būseną dėl AND vartų.

Sinchroninio skaitiklio grandinės schema

Trijų bitų skaitiklio lentelės serija pateikiama žemiau. Pagrindinis šių skaitiklių privalumas yra tai, kad nėra didesnio laiko atidėjimo, nes visi FF yra aktyvuojami lygiagrečiai. Taigi maksimalus šio sinchroninio skaitiklio veikimo dažnis bus žymiai didesnis nei lygiaverčio pulsacijos skaitiklio.

CLK sinchroninių skaitiklių impulsai

Sinchroniniai dešimtmečio skaitikliai

Sinchroninis skaitiklis skaičiuojamas nuo 0-9, panašus į asinchroninį skaitiklį, ir tada vėl perdirbamas nulis. Šis procesas atliekamas varant 1010 būsenas atgal į 0000 būseną. Tai vadinama sutrumpinta seka, kurią gali sukurti žemiau esanti grandinė.

Sinchroninė dešimtmečio skaitiklio grandinės schema

Iš kairės lentelės serijos galime tai pastebėti

- Q0 susieja kiekvieną CLK pulsą

- Q1 keičiasi kito laikrodžio impulsas kiekvieną kartą, kai Q0 = 1 ir Q3 = 0.

- Q2 keičiasi kito laikrodžio impulsas kiekvieną kartą, kai Q0 = Q1 = 1.

- Q3 keičiasi kito CLK impulso metu kiekvieną kartą, kai Q0 = 1, Q1 = 1 ir Q2 = 1 (skaičius 7) arba kai Q0 = 1 ir Q3 = 1 (skaičius 9).

Sinchroninio dešimtmečio skaitiklio seka

Aukščiau nurodytos charakteristikos yra naudojamos su IR vartai arba ARBA vartai . To loginė schema parodyta aukščiau pateiktoje diagramoje.

Sinchroniniai „Up-Down“ skaitikliai

Žemiau pateikiamas trijų bitų sinchroninis „Up-Down“ skaitiklis, lentelių forma ir serijos. Šio tipo skaitiklis turi aukštyn-žemyn valdiklį i / p, panašų į asinchroninį aukštyn-žemyn skaitiklį, kuris naudojamas valdyti skaitiklio kryptį per tam tikrą seriją.

Sinchroninės „Up-Down“ skaitiklių grandinės schema

Lentelės serija rodo

- Q0 susieja kiekvieną CLK impulsą tiek aukštyn, tiek žemyn

- Kai Q0 = 1 aukštesnei serijai, tada kito CLK impulso Q1 būsena pasikeičia.

- Kai Q0 = 0 žemesnėje eilutėje, tada kito CLK impulso Q1 būsena pasikeičia.

- Kai Q0 = Q1 = 1 aukštesnei serijai, tada kito CLK impulso Q2 būsena pasikeičia.

- Kai Q0 = Q1 = 0 žemesnėje eilutėje, tada kito CLK impulso Q2 būsena pasikeičia.

Sinchroninių dešimtmečių skaitiklių seka

Aukščiau nurodytos charakteristikos yra naudojamos vartams AND, OR vartams ir NE vartams. To loginė schema parodyta aukščiau pateiktoje diagramoje.

Skaitiklių programos

Skaitiklių taikymas daugiausia susijęs su skaitmeniniais laikrodžiais ir multipleksu. Geriausias skaitiklio pavyzdys yra lygiagretus toliau aprašytai nuoseklios duomenų konvertavimo logikai.

Bitų rinkinys, vienu metu veikiantis lygiagrečiomis linijomis, vadinamas lygiagrečiais duomenimis. Bitų rinkinys, atliekamas vienoje laiko eilutės eilutėje, vadinamas serijiniais duomenimis. Duomenų konvertavimas iš lygiagrečių į nuoseklius paprastai atliekamas naudojant skaitiklį, kad būtų gaunama dvejetainė duomenų serija, pasirinkite i / ps MUX, kaip paaiškinta toliau pateiktoje grandinėje.

Lygiagrečių eilučių duomenų konvertavimas

Pirmiau pateiktoje grandinėje modulo-8 skaitiklis susideda iš Q o / ps, kurie yra prijungti prie duomenų, pasirinkite i / ps iš 8 bitų MUX . Pirmoji 8 bitų lygiagrečių duomenų grupė taikoma MUX įėjimams. Kai skaitiklis eina per dvejetainę seriją nuo 0-7, kiekvienas bitas prasideda D0, yra nuosekliai parinktas ir perduodamas per MUX į o / p liniją. Po 8-CLK impulsų duomenų baitas buvo pakeistas į serijinį formatą ir išsiųstas per perdavimo liniją. Tada skaitiklis vėl apdoroja 0 ir panašiu procesu vėl keičia nuosekliai kitą baitą.

Taigi, viskas yra apie skaitiklius ir skaitiklių tipus, į kuriuos įeina asinchroniniai skaitikliai, sinchroniniai skaitikliai, asinchroniniai dešimtmečių skaitikliai, sinchroniniai dešimtmečių skaitikliai, asinchroniniai aukštyn-žemyn skaitikliai ir sinchroniniai aukštyn-žemyn skaitikliai. Be to, bet kokios abejonės šia tema ar laikmačiai ir skaitikliai 8051 mikrovaldiklyje komentuokite žemiau esančiame komentarų skyriuje.