Daugikliai naudojami daugybėje skaitmeninių signalų apdorojimo ir kitų programų. Dėl pažangos dabartinėse technologijose daugelis tyrinėtojų daugiausia dėmesio skyrė projektavimo veiksniams, siekdami geresnių rezultatų. Kai kurie projektavimo tikslai yra - didelis greitis, tikslumas, mažas energijos suvartojimas, išdėstymo taisyklingumas, mažesnis plotas. DSP procesorius turi įvairius skaičiavimo blokus, pvz., multipleksoriai, pridėtojai, MAC . Šių blokų veikimo ir vykdymo greitis padidėjo, palyginti su ankstesnėmis versijomis. Daugiklio koeficientas priklauso nuo dviejų veiksnių: puslaidininkių technologija ir daugiklio architektūra. Skaitikliai yra pagrindinis skaitmeninių tankintuvų elementas, kur atliekame pakartotinių papildymų seriją, kad paspartintume daugiklio veikimą, reikia padidinti pridėtojo veikimo greitį. Yra daugybė skaitmeninio signalo apdorojimo programų, kur kritinis uždelsimo kelias ir procesoriaus našumas priklauso nuo daugiklio. Yra daugybė daugiklių, tarp kurių 4 × 4 masyvo daugiklis yra išplėstinis, aprašytas šiame straipsnyje.

Daugybos schemos 4 × 4 masyvo daugikliu

Yra dviejų rūšių daugybos schemos

Serijinis dauginimas („Shift“ - „Add“): Nuoseklinio dauginimo operacija gali būti išspręsta suradus dalinius produktus ir sudėjus dalinius produktus. Įgyvendinimai yra primityvūs ir paprastos architektūros

Lygiagretusis dauginimas: Lygiagrečiai produktai yra generuojami vienu metu lygiagrečiai dauginant ir naudojant didelio našumo mašiną. Lygiagrečiai įgyvendinami, vėluojama iki minimumo.

Daugybos algoritmas

Dauginimo procesą sudaro trys pagrindiniai žingsniai:

- Dalinis produkto generavimas

- Dalinis produkto sumažinimas

- Galutinis papildymas.

Paprastas daugybos metodas yra algoritmas „pridėti ir perkelti“. Žemiau parodytas N bitų daugiklio dauginimo algoritmas.

4 kartus po 4 padauginti

4 - po 4 - daugyba 1

2 pavyzdys

Daliniai produktai generuojami naudojant AND vartus, kur

- Daugkartinis = N bitai

- Daugiklis = M bitai

- daliniai produktai = N * M.

Padauginus du 8 bitų skaičius, gaunamas 16 bitų produktas.

Papildymo lygtis yra

P (m + n) = A (m). B (n) = i = 0 m-1∑ j = 0n-1∑ ai bj 2i + j ……. 1

A, B = 8 bitai

Daugybos žingsniai

Toliau pateikiami bet kokio dauginimo veiksmai

- Jei daugiklio LSB yra „1“. tada pridėkite daugiklį į kaupiamojo daugiklio bitą, kuris perkeliamas vienu bitu į dešinę, o daugkartinis bitas - į kairę.

- Sustokite, kai visi daugiklio bitai bus lygūs nuliui.

- Jei daliniai produktai pridedami nuosekliai, naudojama mažiau aparatūros. Visus PP galime pridėti lygiagrečiuoju daugikliu. Tačiau galima naudoti suspaudimo techniką, prieš atliekant pridėjimą galima sumažinti dalinių produktų skaičių.

Skirtingi daugiklių tipai

Skirtingi daugiklių tipai yra:

Kabinų daugiklis

Stendo daugiklio funkcija yra padauginti 2 pasirašytus dvejetainius skaičius, kurie yra pavaizduoti 2 papildymas forma. Kabinų daugiklių privalumai yra Minimalus kompleksas, dauginimas paspartinamas. Kabinų daugiklių trūkumai yra tai, kad energijos suvartojimas yra didelis.

Kombinacinis daugiklis

Kombinacinis daugiklis atlieka dviejų nepasirašytų dvejetainių skaičių dauginimą. Kombinuoto daugiklio pranašumas yra tas, kad jis gali lengvai generuoti tarpinius produktus. Pagrindinis kombinacinio daugiklio trūkumas yra tai, kad jis užima didelius plotus.

Nuoseklus daugiklis

Dauginimas yra padalintas į žingsnių seką, kur sukurtas dalinis produktas pridedamas prie akumuliatoriaus. Dalinė suma dabar perkeliama į kitą žingsnį. Privalumas yra tai, kad jis užima mažiau ploto. Nuoseklaus daugiklio trūkumas yra lėtas procesas.

Wallace medžio daugiklis

Tai sumažina dalinių produktų skaičių ir naudoja dalinį produktą, jei norite pridėti dalinių produktų. „Wallace“ medžio daugiklio pranašumas yra greitas ir vidutinio sudėtingumo dizainas. Pagrindinis „Wallace“ medžių daugiklio trūkumas yra tai, kad maketo dizainas yra netaisyklingas ir užima didesnį plotą.

Masyvo daugiklis

Daugiklio grandinė remiasi pridėjimo poslinkio algoritmu. Pagrindinis masyvo daugiklio privalumas yra paprastas ir taisyklingos formos. Masyvo daugiklio trūkumas yra vėlavimas yra didelis ir didelis energijos suvartojimas.

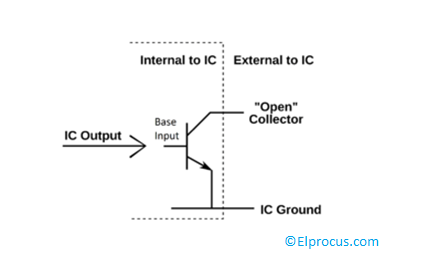

„Shift“ ir „Pridėti daugiklį“

Tai panašu į įprastą daugybos procesą, kurį atliekame matematikoje, iš masyvo daugiklio srauto pokalbio, kur X = daugiklis ir Y = daugiklis A = kaupiklis, Q = koeficientas. Pirmiausia patikrinama, ar Q yra 1, ar ne, jei jis yra 1, pridėkite A ir B ir perkelkite A_Q aritmetinę teisę, kitaip, jei tai nėra 1, tiesiogiai perkelkite A_Q aritmetinę teisę ir sumažinkite N 1, kitame etape patikrinkite, ar N arba ne. Jei N ne 0 pasikartoja nuo Q = 0 žingsnio, nutraukite procesą.

„shift-and-add-multiplier“

4 × 4 masyvų daugiklio konstravimas ir darbas

Masyvo daugiklio projektinė struktūra yra taisyklinga, ji remiasi pridėjimo poslinkio algoritmo principu.

Dalinis produktas = daugiklio ir daugiklio bitai… (2)

kur produktui naudojami AND vartai, sumuojama atliekant „Full Adders“ ir „Half Adders“, kur dalinis produktas perkeliamas pagal jų bitų eiliškumą. Naudojant n * n masyvo daugiklį, n * n AND vartai apskaičiuoja dalinius produktus, o dalinius produktus galima pridėti naudojant n * (n - 2) pilnus ir n Half pridėjus. Parodytas 4 × 4 masyvo daugiklis turi 8 įėjimus ir 8 išėjimus

4-iki-4-masyvo daugiklis

4 × 4 masyvo daugiklio statybiniai blokai

Pilname sumuotajame yra trys įvesties eilutės ir dvi išvesties eilutės, kur mes tai naudojame kaip pagrindinį masyvo daugiklio bloką. Toliau pateikiamas 4 × 4 masyvo daugiklio pavyzdys. Kairiausias bitas yra dalinio produkto LSB bitas.

pridėtinė-blokinė-diagrama

masyvo daugiklio blokinė diagrama

Dešiniausia dalis yra dalinio produkto MSB bitai. Daliniai produktai dabar dauginami pasislinkę kairiosios pusės link ir pridedami, kad gautų galutinį produktą. Šis procesas kartojamas tol, kol nebeliks dviejų dalinių produktų.

4-padauginimas-1

logika-schema-4-by-4 - masyvas - daugiklis

Kai a0, a1, a2, a3 ir b0, b1, b2, b3 yra daugiklis ir daugiklis, visų produktų sumavimas yra dalinis produktas. Dalinio produkto sumos rezultatas yra produktas.

4 × 4 masyvo daugikliui reikia 16 IR vartų, 4 Half Adders (HA), 8 Full Adders (FA). Iš viso 12 pridėtojų.

4 × 4 masyvo daugiklio privalumai

Masyvo daugiklio privalumai yra:

- Mažiausias sudėtingumas

- Lengvai keičiamas

- Lengvai vamzdynais

- Taisyklingos formos, lengvai pastatoma ir nukreipiama

4 × 4 masyvo daugiklio trūkumai

Masyvo daugiklio trūkumai yra šie,

- Didelis energijos suvartojimas

- Daugiau skaitmeniniai vartai todėl susidaro dideli plotai.

4 × 4 masyvo daugiklio programos

Pateikiamos masyvo daugiklio programos,

- Masyvo daugiklis naudojamas atlikti aritmetinė operacija , kaip filtravimas, Furjė transformacija, vaizdų kodavimas.

- Greitas veikimas.

Taigi, viskas yra apie 4 × 4 masyvo daugiklis Tai yra pažangus daugiklis, pagrįstas pridėjimo ir perkėlimo principu, našumą galima lengvai padidinti naudojant paprastos konstrukcijos dujotiekio techniką, nors ji naudoja daugiau loginių vartų, kur juos galima įgyvendinti naudojant „Verilog“. Čia yra klausimas: „Kiek loginių vartų reikia norint sukurti 3 * 3 masyvų daugiklį?“.