Tam tikrą dažnį turinčiam signalui generuoti naudojamas osciliatorius, kuris yra naudingas sinchronizuojant skaičiavimo procesą skaitmeninėse sistemose. Tai yra elektroninė grandinė, gaminanti nuolatines bangos formas be jokio įvesties signalo. Osciliatorius konvertuoja nuolatinės srovės signalą į kintamą signalo formą norimu dažniu. Yra įvairių tipų generatoriai, priklausomai nuo komponentų, naudojamų elektroninėse grandinėse. Skirtingi osciliatorių tipai yra Vienos tilto osciliatorius, RC fazės poslinkio osciliatorius, Hartley osciliatorius , įtampos valdomas osciliatorius, „Colpitts“ osciliatorius , žiedinis osciliatorius, Gunno osciliatorius ir kristalinis osciliatorius ir tt Iki šio straipsnio pabaigos žinosime, kas yra žiedinis osciliatorius, darinys , išdėstymas, dažnio formulė ir programos.

Kas yra žiedinis osciliatorius?

Žiedinio osciliatoriaus apibrėžimas yra „nelyginis skaičius keitiklių, sujungtų nuoseklia forma, turinčiais teigiamą grįžtamąjį ryšį ir išėjimo svyruojančius tarp dviejų įtampos lygių 1 arba 0, kad būtų galima išmatuoti proceso greitį. Vietoj inverterių mes galime tai apibrėžti ir „NOT“ vartais. Šie osciliatoriai turi nelyginį keitiklių skaičių. Pavyzdžiui, jei šis osciliatorius turi 3 keitikliai tada jis vadinamas trijų pakopų žiediniu osciliatoriumi. Jei keitiklio skaičius yra septyni, tai yra septynių pakopų žiedinis osciliatorius. Inverterio etapų skaičius šiame osciliatoriuje daugiausia priklauso nuo dažnio, kurį norime sukurti iš šio osciliatoriaus.

žiedo-osciliatoriaus-diagrama

Suprojektuoti žiedinį osciliatorių galima naudojant tris keitiklius. Jei osciliatorius naudojamas vienpakopiu, tada svyravimų ir stiprinimo nepakanka. Jei osciliatorius turi du inverterius, tada sistemos virpesiai ir stiprinimas yra šiek tiek daugiau nei vienpakopis žiedinis osciliatorius. Taigi šiame trijų pakopų osciliatoriuje yra trys keitikliai, kurie nuosekliai sujungiami su teigiamo grįžtamojo ryšio sistema. Taigi sistemos virpesiai ir padidėjimas yra pakankami. Tai yra priežastis pasirinkti trijų pakopų osciliatorių.

„Žiedinis osciliatorius naudoja nelyginį keitiklių skaičių, kad pasiektų didesnį stiprinimą nei vienas invertuojantis stiprintuvas. Inverteris vėluoja įvesties signalą, o padidėjus keitiklių skaičiui, osciliatoriaus dažnis sumažės. Taigi norimas osciliatoriaus dažnis priklauso nuo osciliatoriaus keitiklio pakopų skaičiaus “.

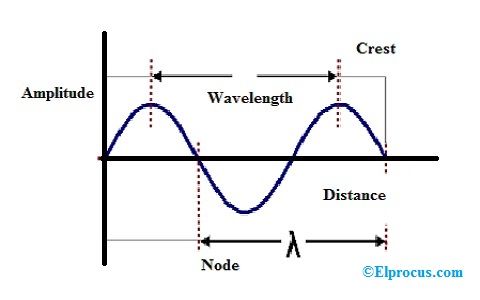

Šio osciliatoriaus svyravimo formulės s dažnis yra

žiedo-osciliatoriaus dažnis

Čia T = vieno keitiklio vėlavimas

n = keitiklių skaičius osciliatoriuje

Žiedinio osciliatoriaus išdėstymas

Aukščiau pateiktose dviejose diagramose parodytos 3 pakopų žiedinio osciliatoriaus scheminės ir išėjimo bangos formos. Čia PMOS dydis yra dvigubai didesnis nei NMOS. NMOS dydis yra 1,05, o PMOS - 2,1

žiedas-osciliatorius-išdėstymas

Iš šių verčių trijų pakopų žiedinio osciliatoriaus laikotarpis yra 1,52ns. Iki šio laikotarpio galime pasakyti, kad šis osciliatorius gali gaminti signalus, kurių dažnio diapazonas yra 657,8 MHz. Norėdami generuoti mažesnį nei šis dažnis signalą reiškia, kad į šį osciliatorių turėtume pridėti daugiau keitiklio pakopų. Tai padidins vėlavimą ir sumažės veikimo dažnį. Pavyzdžiui, norint generuoti 100 MHz arba mažesnio nei dažnio signalus, į šį osciliatorių reikia pridėti 20 keitiklio pakopų.

žiedas-osciliatorius-išvestis2

Žemiau pateiktame paveikslėlyje parodytas žiedinio osciliatoriaus išdėstymas. Tai yra 71 pakopos osciliatorius, skirtas generuoti signalą 27 MHz dažniu. Inverteriai, naudojami šiame osciliatoriuje, sujungiami naudojant kontaktus L1M1 ir PYL1. Su šiuo kontaktu keitiklių įėjimai ir išėjimai yra sujungti. „Vdd“ kaištis skirtas šaltinio prijungimo tikslams.

žiedas-osciliatorius-išdėstymas-71-etapai

Žiedinis osciliatorius naudojant tranzistorių

Žiedinis osciliatorius yra inverterių, sujungtų nuoseklia forma su grįžtamuoju ryšiu, derinys. Ir paskutinės pakopos išėjimas vėl sujungtas su pradiniu osciliatoriaus etapu. Tai galima padaryti ir naudojant tranzistorių. Žemiau pateiktame paveikslėlyje parodyta žiedinio osciliatoriaus implantacija su a CMOS tranzistorius .

žiedinius osciliatorius naudojančius tranzistorius

- Įėjimas į šį osciliatorių gali būti per 6 ir 14 kaiščius, sujungtus su Vdd, ir 7 kaiščius, prijungtus prie žemės.

- C1, C2 ir C3 yra kondensatoriai, kurių vertė yra 0,1 uF.

- Čia kaištis 14, ty turėtų gauti 3,3 V maitinimo įtampą.

- Šio osciliatoriaus išvestis gali būti paimta iš kaiščio 12 prievado.

- Nustatykite Vdd vertę į 3,3 V ir nustatykite dažnį 250 Hz. C1, C2 ir C3 kondensatoriai matuoja kilimo ir kritimo laiką kiekviename keitiklio išėjimo etape. Atkreipkite dėmesį į virpesių dažnį.

- Tada prijunkite Vdd kaištį prie 5 V ir pakartokite aukščiau aprašytą procesą ir užrašykite sklidimo delsos laiką bei svyravimų dažnį.

- Pakartokite procesą su keliais įtampos lygiais, tada galime suprasti, jei maitinimo įtampa padidina vartų vėlavimą (kilimo ir kritimo laikas) sumažėja. Jei maitinimo įtampa sumažėja, vartų vėlavimas didėja.

Dažnio formulė

Remiantis keitiklio etapų skaičiaus naudojimu žiedinių osciliatorių dažnis galima gauti pagal šią formulę. Čia taip pat svarbu kiekvieno keitiklio uždelsimo laikas. Galutinis šio osciliatoriaus stabilus virpesių dažnis yra

Čia n nurodo keitiklio pakopų, naudojamų šiame osciliatoriuje, skaičių. T yra kiekvieno keitiklio pakopos vėlavimo laikas.

Šis osciliatoriaus dažnis priklauso tik nuo vėlavimo laiko etapų ir šiame osciliatoriuje naudojamų etapų skaičiaus. Taigi uždelsimo laikas yra svarbiausias parametras ieškant osciliatoriaus dažnio.

Programos

Keletas šio osciliatoriaus programos bus aptariamas čia. Jie yra,

- Jie naudojami matuojant įtampos ir temperatūros poveikį integruotas lustas .

- Plokštelių bandymo metu pirmenybė teikiama šiems osciliatoriams.

- Dažnio sintezatoriuose šie osciliatoriai yra taikomi.

- Šie osciliatoriai yra naudingi duomenų atkūrimo tikslais nuosekliajame duomenų ryšyje.

- Į fazėje užrakinta kilpa (PLL) VCO gali būti suprojektuoti naudojant šį osciliatorių.

Į žiedinis osciliatorius buvo sukurtas norimam dažniui generuoti bet kokiomis sąlygomis. Svyravimo dažnis priklauso nuo kiekvieno keitiklio pakopų etapų skaičiaus ir uždelsimo laiko. Šio osciliatoriaus temperatūros ir įtampos poveikį galima išbandyti penkiomis sąlygomis. Visomis skirtingomis bandymo sąlygomis, jei temperatūra padidėja, išėjimo laiką galima sutrumpinti, palyginti su mažiausia temperatūros verte. Turime išanalizuoti fazės triukšmą ir virpesių vertę, jei temperatūra kinta.